COMPAQ COMPUTER CORPORATION

DeskPro/M Family

|

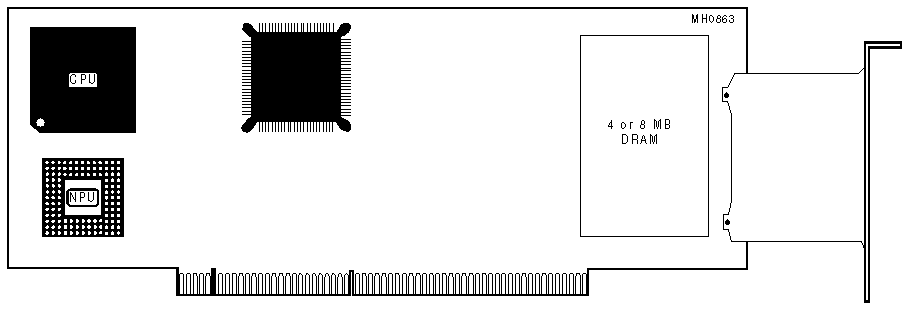

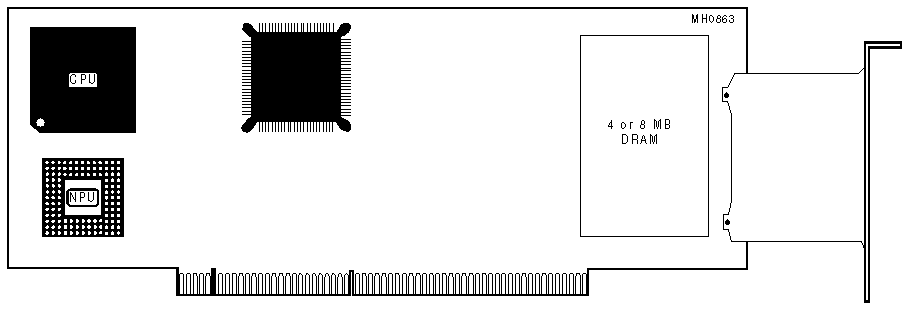

Processor |

80386DX/80486SX/80487SX/80486DX/80486DX2 |

|

Processor Speed |

16/25/33/50(internal)MHz |

|

Chip Set |

Compaq |

|

Max. Onboard DRAM |

64MB (on system processor card and memory card) |

|

Cache |

None |

|

BIOS |

Compaq |

|

Dimensions |

370mm x 125mm |

|

I/O Options |

System processor card slot, proprietary system memory card |

|

NPU Options |

3167/4167 |

|

USER CONFIGURABLE SETTINGS |

|||

|

Function |

Switch |

Position |

|

|

» |

Factory configured - do not alter |

SW500/1 |

Off |

|

» |

EISA configuration unlocked |

SW500/2 |

Off |

|

|

EISA configuration locked |

SW500/2 |

On |

|

» |

Floppy drive read/write enabled |

SW500/3 |

Off |

|

|

Floppy drive read/write disabled |

SW500/3 |

On |

|

» |

EISA configuration used |

SW500/4 |

Off |

|

|

EISA configuration ignored |

SW500/4 |

On |

|

» |

Password check at power-on enabled |

SW500/5 |

Off |

|

|

Password check at power-on disabled |

SW500/5 |

On |

|

» |

EISA configuration saved |

SW500/6 |

Off |

|

|

EISA configuration erased |

SW500/6 |

On |

|

Note:The location of switch on board is unidentified. |

|||

|

CPU TYPE CONFIGURATION |

|||

|

Type |

S1 |

S2 |

S3 |

|

80486SX - no 80487SX installed as NPU |

Off |

Off |

Off |

|

80486SX - 80487SX installed as NPU |

Off |

On |

On |

|

80486DX |

On |

Off |

On |

|

Note:The location of switch on board is unidentified. |

|||

|

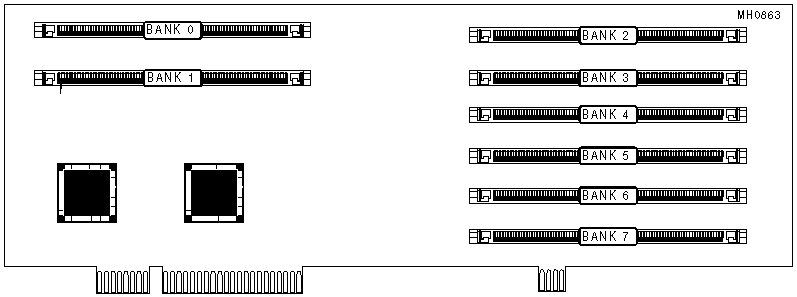

DRAM CONFIGURATION |

||||||||

|

Size |

Bank 0 |

Bank 1 |

Bank 2 |

Bank 3 |

Bank 4 |

Bank 5 |

Bank 6 |

Bank 7 |

|

1MB |

(1)256Kx36 |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

|

2MB |

(1)256Kx36 |

(1)256Kx36 |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

|

2MB |

(1)512Kx36 |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

|

3MB |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

NONE |

NONE |

NONE |

NONE |

NONE |

|

4MB |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

NONE |

NONE |

NONE |

NONE |

|

4MB |

(1)512Kx36 |

(1)512Kx36 |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

|

4MB |

(1)1M x 36 |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

|

5MB |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

NONE |

NONE |

NONE |

|

6MB |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

NONE |

NONE |

NONE |

NONE |

NONE |

|

7MB |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

NONE |

|

8MB |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

(1)256Kx36 |

|

8MB |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

NONE |

NONE |

NONE |

NONE |

|

8MB |

(1)1M x 36 |

(1)1M x 36 |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

|

8MB |

(1)2M x 36 |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

|

10MB |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

NONE |

NONE |

NONE |

|

12MB |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

NONE |

NONE |

NONE |

NONE |

NONE |

|

14MB |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

NONE |

|

16MB |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

(1)512Kx36 |

|

16MB |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

NONE |

NONE |

NONE |

NONE |

|

16MB |

(1)2M x 36 |

(1)2M x 36 |

NONE |

NONE |

NONE |

NONE |

NONE |

NONE |

|

20MB |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

NONE |

NONE |

NONE |

|

24MB |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

NONE |

NONE |

|

28MB |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

NONE |

|

32MB |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

(1)1M x 36 |

|

32MB |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

NONE |

NONE |

NONE |

NONE |

|

40MB |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

NONE |

NONE |

NONE |

|

48MB |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

NONE |

NONE |

|

56MB |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

NONE |

|

64MB |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

(1)2M x 36 |

|

Note: Table shows some example configurations. In practice, banks may be filled with any combination of SIMMs, as long as the banks are filled sequentially from Bank 0 to Bank 7. |

||||||||